ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ ВС, РЕАЛИЗУЮЩЕЙ ПОТОКОВЫЕ ВЫЧИСЛЕНИЯ С КОПИРОВАНИЕМ КОДА

Бабякин Ю.Е.

(Москва, Московский Энергетический

Институт(ТУ),Россия)

Интерес к вычислительным системам потока данных с копированием кода вызван возможностью простой и в то же время эффективной аппаратной реализации этих ВС.

Механизм копирования кода в потоковых вычислениях предполагает для каждой

альтернативы, итерации цикла или вызова процедуры создание отдельного

программного экземпляра указанного фрагмента, что позволяет независимо

обрабатывать соответствующие наборы входных токенов. Таким образом,

использование механизма копирования кода способствует реализации значительного

программного параллелизма.

При разработке концепции ВС, для описания потоковых программ использовался язык акторных сетей [1]. В этой модели выделены два вида акторов – функциональные, которые несут в себе информацию о функциях преобразования данных, и активирующие, которые содержат адреса статических сетей, подставляемых в динамическую сеть в зависимости от данных на управляющем входе активирующего актора.

Соответственно,

двум видам акторов в потоковой ВС сопоставлены два вида специализированных

процессоров – F-процессоры и A-процессоры. В качестве

среды для хранения и передачи данных используется многопортовая память с

последовательным доступом [2], на эффективность применения которой для

различных вариантов структур ВС, указано в [3]. Память также специализирована,

то есть акторы хранятся отдельно от токенов, причем модулей памяти, используемых

для хранения информации того и другого типа, может быть несколько.

Каждый процессор

имеет доступ к содержимому памяти через один или несколько портов, осуществляя

ассоциативное считывание и запись информации, которая в данный момент

функционирования системы находятся в ячейке, к которой подключен порт. Информация

в ячейках меняются циклически и через каждый порт за один цикл проходит содержимое

всех ячеек памяти.

Работа потоковой

ВС построена следующим образом. У акторов в поле «признак готовности»

содержится информация о количестве неготовых токенов. F-процессор считывает

«готовый» функциональный актор – все токены которого уже есть в памяти токенов

системы, и удаляет его из акторной памяти. Далее процессор считывает все

входные токены этого актора. Когда все данные собраны, процессор выполняет

операцию над данными. Результаты записываются в память, в соответствующие выходные

токены актора. Если у токенов выставлен признак уведомления, то это значит, что

необходимо уменьшить признак готовности акторов-приемников, для которых эти

токены являются входными. Процессор просматривает акторную память и уменьшает

признаки готовности.

А-процессор

считывает «готовый» активирующий актор, получает входной управляющий токен и в

зависимости от его значения выполняет подстановку сети, а именно: загружает в

память токены и акторы активируемой статической сети, «сшивая» входы и выходы

ее акторов с входами и выходами акторов динамической сети, уже существующей в

системе. Если у выходных токенов активирующего актора был установлен признак

уведомления, то у акторов, для которых эти токены являются входными, процессор

уменьшает признак готовности.

Таким образом,

в работе процессоров потоковой ВС можно выделить пять основных режимов:

– ожидание

готового актора;

– сбор токенов

готового актора;

– вычисление

функции преобразования данных (для F-процессора);

– запись

результатов (для А-процессора – загрузка сети в память);

– уменьшение

признака готовности у ассоциированных по выходам акторов.

В случае

последовательного выполнения выделенных выше действий, процессор львиную долю

времени будет тратить на ожидание данных и ввод-вывод. Однако можно выделить

группы действий, которые связываются в конвейер, и которые можно выполнять

параллельно: ожидание актора и сбор токенов, выполнение функции, запись

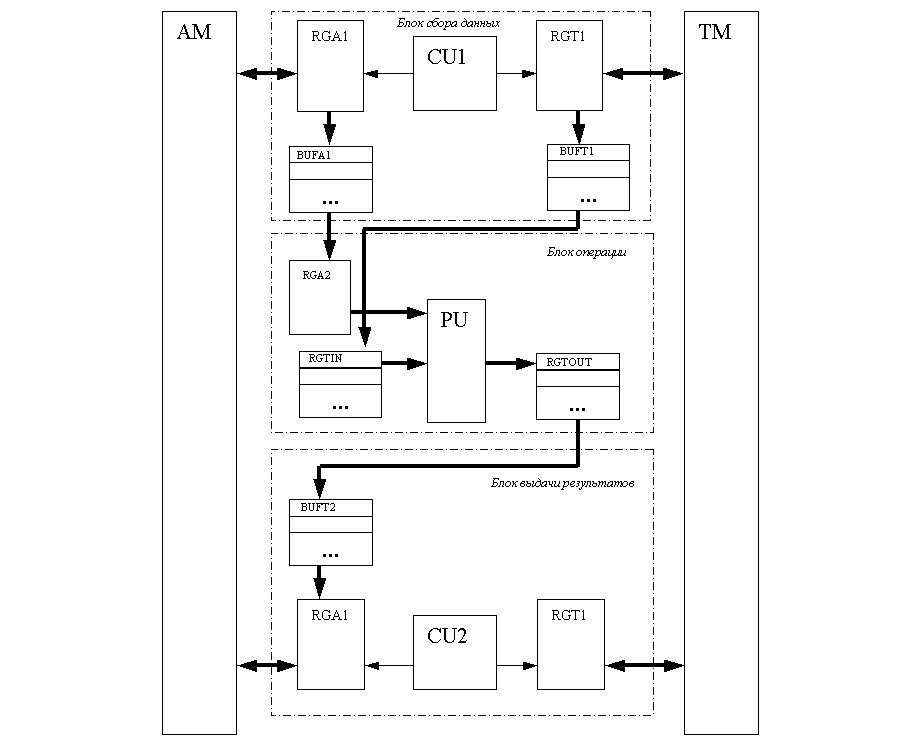

результатов и уменьшения признака готовности. Следовательно, и в архитектуре

процессора можно выделить три блока: блок сбора данных, блок функционального

преобразования (операции), блок выдачи результатов.

Ниже приводится

обобщенная структура процессора потоковой ВС. В качестве примера выбран более

простой F-процессор (рис. 1). Указанные выше блоки выделены

на рисунке штрих-пунктирными линиями.

Рис. 1. Структура F-процессора потоковой ВС

Блок сбора данных сканирует память, получая значение текущей ячейки памяти акторов AM, проходящей через порт, в регистр RGA1, а памяти токенов TM – в RGT1 (CU1 – устройство, управляющее операциями работы с памятью). Готовый актор помещается в BUFA1, а все его входные токены в BUFT1. По мере готовности блока операций, данные выдаются ему в RGA2 и RGTIN, а блок сбора данных продолжает сканировать память. В блоке операций выполняется преобразование данных (некоторым процессорным устройством – PU), результат которого выдается в RGTOUT. Блок операций выдает данные выходных токенов в BUFT2 блоку выдачи результатов, по мере его готовности, последний сканирует память (управляется CU2), записывая данные в соответствующие ячейки.

Если каждый блок процессора имеет свой порт доступа к памяти, то это дополнительно уменьшится время, затрачиваемое на получение данных, особенно, когда число процессоров невелико по сравнению с емкостью памяти.

Дополнительное повышение скорости получения готовых акторов и токенов дает организация дополнительных блоков сбора/ выдачи и очередей на входе/ выходе блока операций (кэширование). При этом следует учесть, что мы используем последовательную память и в общем случае размер кэша (число блоков) прямо зависит от емкости блоков памяти в ячейках и обратно зависит от среднего времени выполнения операции в тактах чтения ячейки памяти.

Предлагаемые принципы построения процессоров направлены на достижение максимальной эффективности использования многопортовой памяти с последовательным доступом для организации потоковых вычислений с копированием кода.

ЛИТЕРАТУРА

1. Ладыгин И.И., Мороховец

Ю.Е., Калинина Г.А. Акторные сети – язык описания потоковых вычислений. //

Доклады МК «Информационные средства и технологии», том 1. – М.: Изд-во

«Станкин», 1996. – с. 18-23.

2. Мороховец Ю.Е. Ассоциативная конвейерная память и организация вычислений в многопроцессорных ВС. //Доклады МК «Информационные средства и технологии», том 1. – М.: Изд-во «Станкин», 1998. – с.35-40.

3. Иванова О.В. Применение ассоциативной конвейерной памяти для организации потоковых вычислений в многопроцессорных вычислительных системах. //Доклады МК «Информационные средства и технологии», том 2. – М.: Изд-во «Станкин», 2000. – с.106-109.